In ARM srchitecture, there are several processor modes provided for safty issues. Except user mode, other six modes are called "priviledge mode". And except user mode and system mode, other fives are also called "exception mode"[8]. This is shown in Table 3-1.

User mode: Application usually runs in the user mode (except system mode since ARMv4). In user mode, the memory access is restricted. For example, you are not allowed to access the memory where OS kernel is stored[7]. And you also cannot write CPSR register. Hardware devices cannot be read directly in user mode.

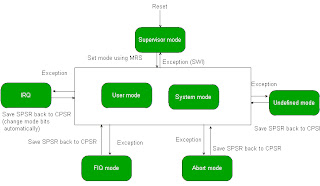

So here when you start up the system(i.e. 2440init.S) as surpervisor mode and go to user mode, you can only enter other modes by exceptions because we cannot change the content of CPSR in user mode(see figure 2-6). For example, you can use SWI to enter supervisor mode. An interrupt signal exception change mode into IRQ or FIQ.

Supervisor mode(SVC mode): It is mainly used by SWIs and the OS [3]. In this mode, you can access all the resources of system such as memory, CPSR, hardware devices and so on. So in OS, usually system call is executed in SVC mode[4], so you have to use SWI to enter system call.

System mode: It debuts since ARMv4. It is simlilar to user mode except it can access all the resources, so it is used to develop nonOS program. You can enter any mode in system mode by instructions MRS and MSR directly.

Summary: There are two ways to change the processor modes: use instructions MRS and MSR(excluding User mode) or through exceptions. And the usual procedure of ARM program execution is shown in below.

Reference:

[1] ARM official document, "Using the arm assembler", P12(total)

[2] Registers and processor modes, http://www.heyrick.co.uk/assembler/regs.html

[3] http://stackoverflow.com/questions/478929/user-mode-vs-supervisor-mode

[4] http://en.wikipedia.org/wiki/System_call#Processor_mode_and_context_switching

[5] 第三篇 ARM7的模式, http://hi.baidu.com/ch314156/blog/item/ad59333aac346bee828b13ff.html

[6] http://zhidao.baidu.com/question/238424160.html

[7] http://topic.csdn.net/u/20091222/15/31840752-81bc-4520-88c2-2f740ecd046e.html

[8] http://zhidao.baidu.com/question/24036020.html?fr=qrl&cid=89&index=1&fr2=query

No comments:

Post a Comment